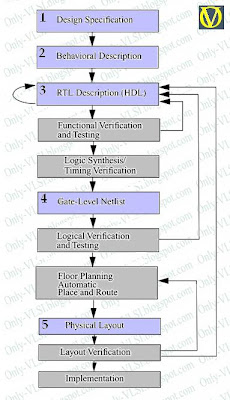

The VLSI IC circuits design flow is shown in the figure below. The various level of design are numbered and the gray coloured blocks show processes in the design flow.

Specifications comes first, they describe abstractly the functionality, interface, and the architecture of the digital IC circuit to be designed.

Specifications comes first, they describe abstractly the functionality, interface, and the architecture of the digital IC circuit to be designed.

Specifications comes first, they describe abstractly the functionality, interface, and the architecture of the digital IC circuit to be designed.

Specifications comes first, they describe abstractly the functionality, interface, and the architecture of the digital IC circuit to be designed.- Behavioral description is then created to analyze the design in terms of functionality, performance, compliance to given standards, and other specifications.

- RTL description is done using HDLs. This RTL description is simulated to test functionality. From here onwards we need the help of EDA tools.

- RTL description is then converted to a gate-level netlist using logic synthesis tools. A gate-level netlist is a description of the circuit in terms of gates and connections between them, which are made in such a way that they meet the timing, power and area specifications.

- Finally a physical layout is made, which will be verified and then sent to fabrication.

Comments